各位先進大家好,小弟目前是使用LabVIEW的菜鳥,目前被派來利用FPGA (型號:USB-7855R),實現Phase modulation 與 phase demodulation (PGC demodulation)。

整體上是要使用FPGA 達到相位調變與解相位調變的功能。

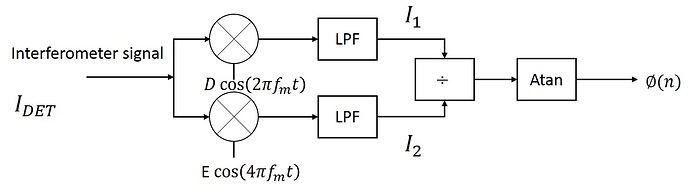

整個解調流程圖如下:

Phase modulation:

硬體上是一個干涉儀架構,利用7855R的AO送出一固定頻率與振幅的弦波電壓給調至參考臂的元件(EOM),達到公式(1)

I=A+B cos(∅+C(cos(2πfmt))

I 是會送入解調流程的訊號,A與B是干涉訊號的直流項、交流項,C與AO送出的弦波電壓值相關,fm是調制頻率,就是AO送出的弦波的頻率。

Phase demodulation :

將I送入解調流程裡,將I分別跟解調流程中的兩個弦波產生器相乘(Mixer),一個弦波產生器以fm頻率產生訊號,另一個產生器以兩倍fm頻率產生弦波訊號,再經過低通濾波器後相除作反正切運算就可以得到相位(phase)∅。

目前小弟對於此技術的基本原理熟悉,但是利用FPGA實現就遇到問題。

整理如下:

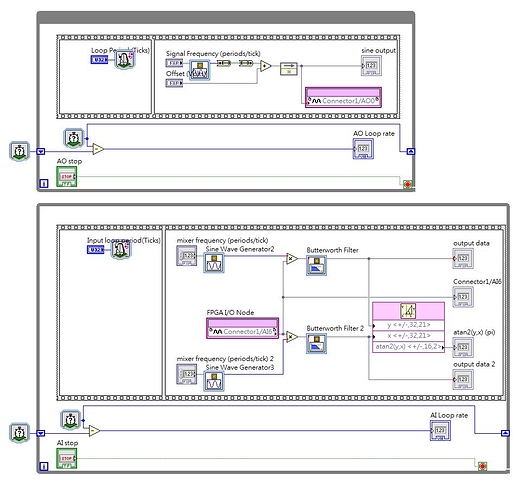

1.目前AO 是利用 FPGA 的 sine wave generator 產生弦波訊號,並輸出電壓。

2. 同一套儀器的AI 收訊號進來做解調變運算

3. 調變結果不合理。理想上調變結果(I1 及 I2 )需要是一振幅固定的弦波,但在2倍頻部分的振幅震盪非常大,導致最後的相位∅失真。

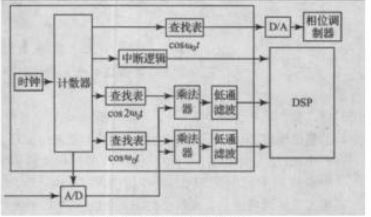

目前已閱讀過相關資料,主要關鍵字是數位PGC解調系統、 Digital PGC demodulation

我目前是根據查到的大陸paper資料邏輯去寫的,如下圖:

目前小弟猜測解調失敗的原因:

1.可能是clock 問題

AO使用一個產生器,解調流程使用兩個產生器,原理上,這三個產生器之間的弦波頻率關係需要是

嚴格的1:1:2。若是比例不穩定或是有差就會解調失敗。

2.在讀過的相關資料裡,有提到需要考慮設置三個clock 1.FPGA 2.DAC 3.ADC

但小弟對電路與電子相關知識不足,從到這裡開始不知道如何操作。

猜測DAC clock 應該會影響AO輸出的弦波頻率。

FPGA 影響解調流程中兩個訊號產生器的弦波頻率。

ADC 是影響擷取頻率。

總結目前狀況:

小弟對原理熟悉,但不知道將原理轉成數位實現時,實際要考慮甚麼因素,以及實現數位化時,應該要注意甚麼細節。

以下是我的VI資料夾

https://drive.google.com/drive/folders/1lCmrn2A-NS8IXaiNrHdvC3hmmm_B67F7?usp=sharing

謝謝!!